# Thermal Conductivity of Suspended Si Nanostructures: Design and Fabrication

J. Rodríguez-Viejo<sup>1</sup>, L. Licea-Jiménez<sup>2,3</sup>, S.A. Pérez-García<sup>2,3</sup> and J. Alvarez-Quintana<sup>2,3,\*</sup>

<sup>1</sup>Nanomaterials and Microsystems Group. Physics Department. Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain

<sup>2</sup>Centro de Investigación en Materiales Avanzados S. C. Unidad Monterrey-PIIT 66600 Apodaca, N. L. México

<sup>3</sup>GENES-Group of Embedded Nanomaterials for Energy Scavenging-CIMAV S.C

**Abstract:** It is presented a process for engineering suspended Si nanostructures in order to measure the thermal conductivity in Si thin films and nanowires based on standard photolithographic techniques. Unlike previous works where the nanostructure was typically grown *ex situ*, and then mechanically placed and contacted between the two microheaters which introduce a contact thermal resistance that difficult an easy interpretation of the experimental results by increasing the uncertainty of the measured thermal conductance of the nanostructure; in this research, the nanostructure is defined from silicon-on-insulator wafers *via* FIB with the objective to minimize the thermal contact resistance between the nanostructure under test and the heat sources. It has been demonstrated by experimental measurements that this suspended device is well adapted for the measurement, control and analysis of the thermal conductivity of nanoscale Si thin films and nanowires. FIB micro-fabrication strategy could be used to obtain Si based nanostructures with very low thermal conductivity which is a desirable characteristic in thermoelectric applications for thermal energy harvesting and solid state refrigeration as well.

Keywords: Si Nanostructures, Thermal Conductivity, Nanoscale Heat Transfer.

## **1. INTRODUCTION**

While two dimensional single crystal semiconductors are attracting much attention due to their promising electrical and thermal properties, one dimensional structure such as nanowires might possess even more desirable characteristics and further improve device performance.

An extremely wide range of applications is conceivable for single crystalline semiconductor nanowires, including not only nano-size electronic devices, but also components for medical applications as well as nano-electromechanical components such as coils, arms, shafts and motors used in MEMS and NEMS systems [1, 2].

Thermal conductivity studies in semiconductor nanowires are of fundamental interest due to the appearance of unusual phonon transport phenomena caused by size confinement effects. The potential range of applications is also driven to significant research due to current microelectronic devices are quickly moving into the low-nanometer regime and the corresponding thermal design urgently needs experimental validation of the thermal behavior of the materials at the nanoscale. micro-devices for thermal conductivity measurements in 1-D systems. The structure consists of two suspended micro-hot plates or coils which are connected by a nanowire. The heaters are isolated from the Si frame through very long SiNx beams [3]. In this type of structures, one of the coils is used as a heater to generate a small amount of heat and the other one is used as a thermometer to detect the heat transferred through the nanowire. The nanowire is typically grown ex situ by using Vapor-Liquid-Solid methods or similar, mechanically placed and then contacted between the two micro-heaters by depositing an amorphous carbon film. This procedure introduces a thermal contact resistance that difficult an easy interpretation of the experimental results. In nanowires, the heat transport through the wire is proportional to the square of the diameter, while the contact conductance is only linearly proportional to the diameter. Therefore, the contact thermal resistance may dominate the total thermal resistance which increases the uncertainty of the experimentally measured thermal conductance of the nanowire. Furthermore. the low thermal conductivity of amorphous carbon thin films might induce a nonnegligible temperature drop in contact regions with the nanowire, which could difficult even more a reliable estimation of the intrinsic thermal conductance of the nanowire. Some experimental results obtained in such systems report uncertainties at least of 15% because of

Previously, other groups have developed specific

<sup>\*</sup>Address correspondence to this author at the GENES-Group of Embedded Nanomaterials for Energy Scavenging-CIMAV S.C; Tel: +52 (81) 11560829; Fax: +52 (81) 1156 0820; E-mail: jaime.alvarez@cimav.edu.mx

the thermal contact resistance, but it could be higher than that value [3, 4].

The aim of our work is to create a device based on suspended nanostructures to measure the thermal conductance in single-crystalline silicon nanowires. Unlike previous works the nanowire will be defined by nanofabrication techniques, starting from silicon-oninsulator wafers, with the objective to minimize the thermal resistance. While this structure is more complicated to fabricate its realization will permit a better estimation of the thermal conductance along the nanowire [5].

### 2. THERMAL MODELING AND MICROFABRICA-TION OF THE SUSPENDED DEVICE

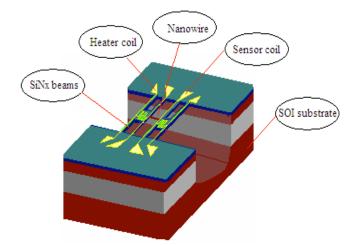

Figure **1** shows a schematic picture of the proposed suspended device. It basically consists of two suspended Pt micro-coils electrically isolated between them but thermally bridged by the silicon nanowire. In the device, one of the coils is used as a heater to generate heat and the other one is used as a thermometer to detect the heat transferred through the nanowire. The two suspended coils are supported by SiNx arms which also serve to electrically isolate the metallic heaters from the silicon chip.

Figure 1: Schematic diagram of the proposed suspended device.

The heating and sensing coils are powered with dc current and, therefore, heat losses by radiation and conduction through the arms have to be considered. To minimize losses by conduction a suitable thermal design of the device is an important starting point before any attempt to microfabrication of the device.

When a dc current is applied to the Pt coil a Joule heat  $Q_h$  is generated. A fraction of this heat  $Q_b$  will be

dissipated to the surroundings through the four SiNx/Pt beams, another part  $Q_w$  will flow through the Si nanowire to the sensing coil and the rest of the heat will be loosed by radiation  $Q_r$ .

By means of a finite element modeling software (COMSOL Multiphysics), the system in Figure 1 is modeled using several lengths and thickness of the SiNx/Pt beams, as well as different Pt coils shapes to obtain the desired structure with minimal conduction losses. Although conduction losses through the heater coil beams will be larger than the conduction heat through the nanowire, the temperature drop on the nanowire can be controlled by the thermal conductance of the beams, thus an appropriate design of the beams is crucial. For instance, beams which are excessively long will have a very high thermal resistance, and therefore the thermal drop on the beams will be significantly larger than in the nanowire, rendering difficult an accurate measurement. Conversely, beams which are too short might increase the temperature drop on the nanowire but could also increase significantly heat losses by conduction into the surroundings. Under those assumptions, a thermal resistance for the beams from twofold to threefold larger than the thermal conductance of the nanowire is attempted. This condition is stated in order to obtain a temperature drop on the nanowire around 25% of the total temperature drop on the beams.

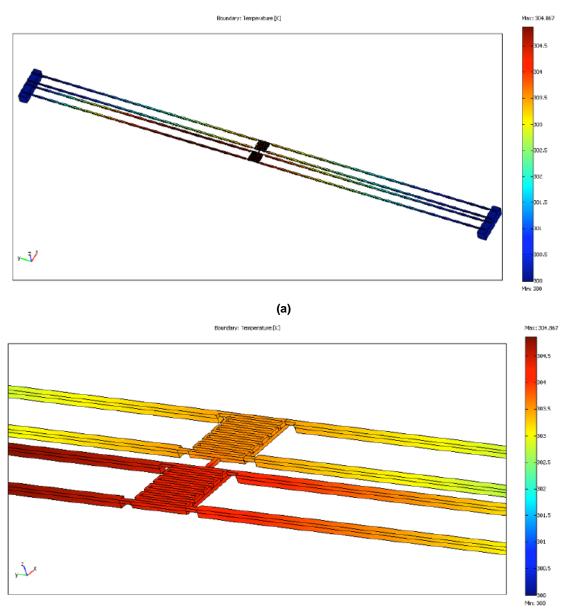

Figure 2a shows the FEM modeling of the whole suspended device. The ends of the beams are linked to the silicon chip frame; the rest of the system is completely suspended. For clarity, Figure 2b shows a zoom from the central part of the device, where the Si nanowire is bridging the heating and sensing coils. It is clear that the temperature profile in the heating and sensing region could be considered constant which permits the measurement of a temperature drop across the Si nanowire. A predefined reduced value of the thermal conductivity due to the size effect in this subdomain is employed for the calculations. The modeling is only used to get a general insight about the optimal geometries and dimensions to minimize heat conduction losses for the physical design and fabrication of the device. Convection heat losses are not considered because the measurements are done under high vacuum conditions around 2.5x10<sup>-7</sup> mbar. However, radiation effects may significantly affect the measurements.

(b)

Figure 2: a: FEM modeling result of the suspended device at 300K. b: FEM modeling result of the suspended device at 300K.

reached by the heating and sensing coils, respectively, once a current  $l_h$  is applied on the heating coil. The heat flows by conduction ( $Q_c$ ) and radiation ( $Q_r$ ) between the two coils by the Fourier and Stefan-Boltzmann laws, respectively, and are given by:

$$Q_c = \frac{T_h - T_s}{R_w} \tag{1}$$

$$Q_r = \varepsilon \sigma A \left( T_h^4 - T_s^4 \right) \tag{2}$$

where  $R_w$  is the thermal resistance of the Si wire,  $\varepsilon$  is the emissivity,  $\sigma = 5.67 \times 10^{-8} \text{ W/m}^2 \text{K}^4$  is the Stefan-Boltzmann constant and *A* is the total area of the hot body, here the area of the heating membrane.

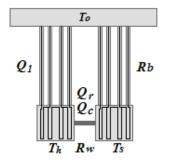

Figure 3: Simple model used to calculate heat and radiation transfer between coils.

Figure **3** shows the schematics of the design. The temperature drop across the nanowire is  $\Delta T_w = T_h - T_s$ , where  $T_h$  and  $T_s$  are the steady state temperatures

By a simple analysis of Figure **3**, the heat conduction  $Q_c$  is also given by:

$$Q_c = \frac{\left(T_h - T_o\right)}{R_w + R_b} \tag{3}$$

where  $R_b$  is the total thermal resistance of the four beams including the Pt and SiNx layers, ( $R_b$ =  $R_{SiNx} || R_{Pt}$ ).

Therefore, the temperature in the sensing coil is:

$$T_s = T_h - \frac{R_w \left(T_h - T_o\right)}{R_w + R_b} \tag{4}$$

Finally, after some algebra and substituting equation (4) into equation (2); the heat transfer by radiation between hot and cold coils is:

$$Q_r = \varepsilon \sigma A \left( 4T_h^3 \Delta T_w - 6T_h^2 \Delta T_w^2 + 4T_h \Delta T_w^3 - \Delta T_w^4 \right)$$

(5)

where  $\Delta T_w$  is also defined by equation (4) as a function of the environment temperature and the temperature of the heating coil.

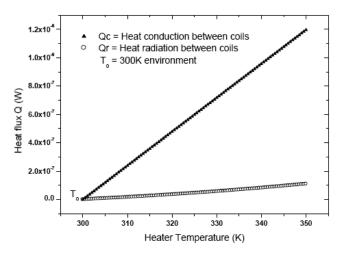

Figure **4** shows the heat current by conduction given by equation 3 (solid symbols) and by radiation given by equation 5 (open symbols) between both coils as a function of the temperature in the heater coil; here, the surroundings are at  $T_o=300$  K. The heat flowing by conduction through the Si nanowire is larger than the heat flowing by radiation between the heating and sensing coils. This behavior is clearly observed in the calculated plots for heat conduction and radiation through the nanowire. It is also noted that to keep heat radiation losses below 5%, the temperature gradient at 300 K needs to be always below 7 K or less according to the predictions. Results on Figure **4** are obtained by

using the black body radiation theory instead of grey body. This is done to predict the maximum losses by radiation.

Figure 4: Heat transfer by conduction and radiation through the Si wire and between coils respectively.

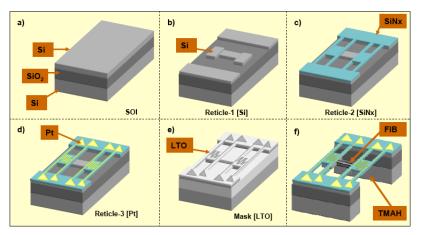

Once the approximated thermal design and the geometrical dimensions of the device are estimated, the next step is to establish the different steps associated to the microfabrication process. The device is batch fabricated using a SOI wafer stage microfabrication process. Because wires of different diameters will have to be measured the starting point is to reduce the initial silicon thickness by thermal oxidation and then etching with HF. This process is repeated several times to achieve the desired thicknesses. The steps of the microfabrication process are schematically presented in Figure **5**.

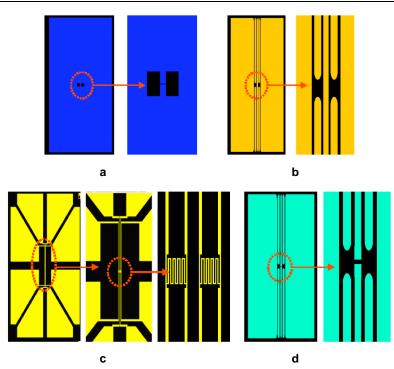

The 3 reticles and 1 mask used during the different stages of the microfabrication process were designed using Lasi design software. Figure **6** shows the various sets of reticles and the mask. Figure **6a** shows the reticle to define the area of the micro-heaters and Si

Figure 5: Microfabrication process for the suspended device.

Figure 6: Reticles and mask designs used during microfabrication process of the suspended device.

nanowire, the area of heaters is 20  $\mu$ mx20  $\mu$ m and the length of nanowire ranges from 1.5  $\mu$ m to 9  $\mu$ m. Figure **6b** presents the reticle used to define the SiNx beams that support the heating and sensing coils. Figure **6c** shows the reticle to define the two micro-heaters and their corresponding 8 connection pads, four pads to each Pt coil because the measurements are done in four point configuration. Figure **6d** shows the mask design that was used to protect the SiNx beams and coils with a Low-Thermal Oxide layer (LTO), during the chemical etching for the final suspension of the structure. The SiNx beams are 450  $\mu$ m long and 3  $\mu$ m wide, the total length of the suspended device is 900  $\mu$ m.

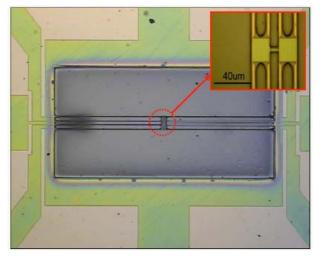

Figure 7: Pictures of the device after TMAH process.

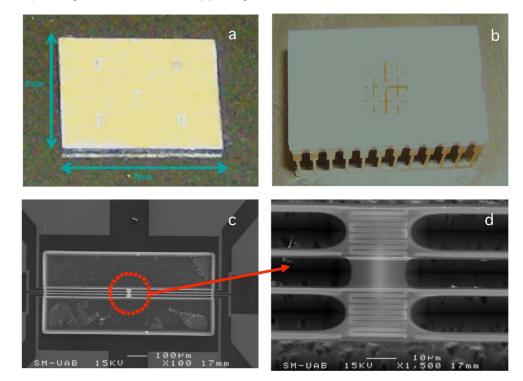

Figure 7 shows an optical image of one of the devices after TMAH process. The wire presented here has a cross section of 100 nm x 1 $\mu$ m and a length of 9  $\mu$ m as shown in the inset. Finally, the diameter of the wire is reduced to the desired value by using focused ion beam (FIB) to produce square or rectangular nanowires.

### 3. MEASUREMENT MECHANISM AND EXPERIMEN-TAL SET UP

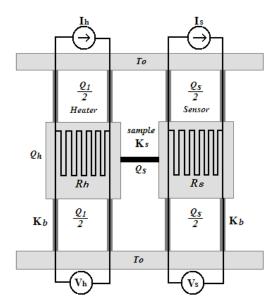

Figure 8 shows a diagram of the experimental setup to measure the thermal conductivity of the Si nanowire. Measurements are carried out in a cryostat in the temperature range from 30 K to 400 K under a vacuum level of  $2.5 \times 10^{-7}$  mbar in order to reduce heat convection. Each coil behaves as a Platinum resistance thermometer. Therefore, by applying a dc electrical current  $I_h$  through the heater coil, a Joule heating given by  $Q_h = l^2 R_h$  will be produced on this coil. Moreover, the resistance of each coil lead is  $R_{l}$ , thus the Joule heating due to this two leads is  $2Q_{I}=2l^{2}R_{I}$ . At this point it is possible to affirm that a certain quantity of heat flow  $Q_s$  is conducted through the Si wire from the heater membrane to the sensor membrane, raising the temperature of the sensor membrane to  $T_s$  and the temperature of the heater membrane to  $T_h$ . Therefore, it is possible to assume that the temperature of the heater coil and sensor coil rise to two uniforms temperatures  $T_h$  and  $T_{s}$ , respectively. This assumption

can be justified because the thermal resistance of the membranes is much smaller than the thermal resistance of the SiNx beams and the Si nanowire.

**Figure 8:** Diagram for the experimental set-up for the thermal conductivity measurements of the Si thin films and nanowires.

As explained before and from the results of thermal modeling in vacuum and with  $\Delta T_h = (T_h-T_o) < 7K$ , the heat transfer between two membranes by air conduction and radiation is negligible compared to  $Q_s$ . Heat flow Qs is further conducted to the environment (Silicon chip frame) through the four beams supporting

the sensor membrane. The rest of heat  $Q_1 = Q_h + 2Q_l - Q_s$ , is conducted to the environment through the other four beams supporting the heater membrane. The four beams supporting each of the membranes are designed to be identical, then the total thermal conductance of the four beams is defined as  $K_b = 4k_{eff}A/I = R_b^{-1}$  where  $k_{eff}$  is made up for the individual thermal conductivities of the SiNx and Pt, *A* is the cross section and *I* the length of the beam. From Figure **8** the heat  $Q_s$  flowing through the Si nanowire:

$$Q_s = \frac{T_h - T_s}{R_w} = \frac{T_s - T_o}{R_b}$$

(6)

where  $R_w = K_s^{-1}$  is the thermal resistance (the inverse is the thermal conductance  $K_s$ ) of the nanowire.

And therefore:

$$R_w = R_b \frac{T_h - T_s}{T_s - T_o} \tag{7}$$

Furthermore, from the same Figure 5.14, the thermal resistance of the beams is given by:

$$R_b = \frac{T_h - T_o}{Q_1} \tag{8}$$

By substituting  $Q_1 = Q_h + 2Q_l - Q_s$  where  $Q_s$  is defined by equation (6) into equation (8):

Figure 9: Suspended 50 nm thick Si film nanostructure used to measure the thermal conductivity.

Thermal Conductivity of Suspended Si Nanostructures: Design and Fabrication Journal of Advanced Thermal Science Research, 2015, Vol. 2, No. 1 7

$$R_{b} = \frac{(T_{h} - T_{o}) + (T_{s} - T_{o})}{Q_{h} + 2Q_{l}}$$

(9)

By redefining the quantities  $\Delta T_h = T_h - T_o$  and  $\Delta T_s = T_s - T_o$  equations (9) and (7) can be rewritten as:

$$R_b = \frac{\Delta T_h + \Delta T_s}{Q_h + 2Q_l} \tag{10}$$

$$R_{w} = R_{b} \frac{\Delta T_{h} - \Delta T_{s}}{\Delta T_{s}}$$

(11)

The thermal resistance of the beams  $R_b$  can be experimentally obtained from equation (10);  $Q_h$  and  $Q_l$  can be calculated readily from the input  $I_h$  dc current and the electrical resistance of the heater coil and Pt leads, respectively.  $\Delta T_h$  and  $\Delta T_s$  are calculated from the measured resistance of the two coils and their temperature coefficient of the resistance (TCR),  $\alpha = \frac{1}{R} \frac{dR}{dT}$ .

Finally, the thermal resistance of the nanowire  $R_w$  is obtained by using equation (11) and the obtained value of  $R_b$  as well as  $\Delta T_h$  and  $\Delta T_s$ . At this point, from the value  $R_w$  and the geometric parameters of the nanowire, the thermal conductivity of the Si nanowire is obtained.

# 4. THERMAL CONDUCTIVITY OF A SUSPENDED SILICON THIN FILMS AND NANOWIRES

As a proof-of-concept of the suspended structures an ultrathin Si layer with thickness of 50nm and length of 10µm bridging the two heaters was used to measure the thermal conductivity at 300 K. Figure **9a** shows the four suspended structures that are placed on every chip. The whole chip mounted onto the ceramic chip holder is shown in Figure **9b**. Figure **9c** is a SEM micrograph of the suspended device with the four SiNx beams holding the two sensors. Figure **9d** is a zoom that clearly shows the two sensors connected by the ultra-thin silicon film.

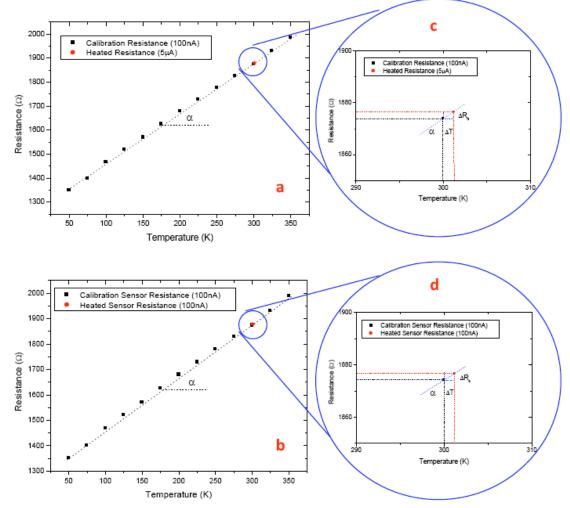

Figure 10: Experimental calibration curves obtained for, a) and c) the heating coil and b) and d) sensing coil.

Afterwards, we follow the procedure previously described in order to measure the temperature coefficient of resistance of the heating and sensing coils in the range 50K to 350 K. Basically, a current of 100 nA is used to minimize Joule heating and obtain the voltage drop across the metal resistor. The same procedure is performed to obtain the calibration curve for the sensing coil. Figures 10a and 10b are the experimental calibration curves obtained for the heating and sensing coils, respectively. From the curve's slopes an experimental value for the temperature coefficient of resistance (TCR),  $\alpha \sim 1.1 \times 10^{-3} \text{K}^{-1}$  was measured. Next, in order to produce self-heating a 5µA dc current was applied on the heating sensor and the electrical resistance was then measured. Figure 10c shows a zoom to highlight the resistance increase due to the higher applied current. Simultaneously, a 100 nA dc current was also applied on the sensing coil to sense the resistance change due to the heat transferred from the heating coil through the silicon ultrathin membrane into it. Figure 10d shows a zoom for the corresponding resistance increment.

The infinitesimal changes on the resistance and temperature dR/dT in the temperature coefficient of resistance  $\alpha$  can be approximated to increments  $\Delta R/\Delta T$  due to the high linearity of dR/dT in the temperature range of 50K to 300K. Therefore, the TCR becomes:

$$\alpha = \left(\frac{1}{R_0}\right) \left(\frac{R_0 - R_i}{T_0 - T_i}\right) = \left(\frac{1}{R_0}\right) \left(\frac{\Delta R_i}{\Delta T_i}\right)$$

(12)

where Ri refers to the resistance of the heating or sensing coils during heating and  $R_0$  is the resistance at steady state temperature, i. e. at 300 K in this specific case.

From equation (12) the temperature increments due to the heating current can be obtained for both the heating coil ( $\Delta T_h$ ) and sensing coil ( $\Delta T_s$ ).

Table **1** shows the corresponding variations in resistance and temperature obtained for both coils. These values are also used to calculate the thermal conductivity of the silicon membrane by using equations (10), (11) and the dimensions of the film. It is

necessary to note that values on Table **1** are an average over 3 measurements. The uncertainty is the standard deviation of the measure. The time estimated to get a stable resistance measurement depends on the time required by the cryostat to achieve a predetermined steady state temperature, this ranges between one and two hours.

From the values in Table 1, a thermal conductivity value k~40.3 W/m\*K is obtained for the 50 nm thick suspended silicon membrane. Furthermore, an uncertainty of  $\pm$  2.41 W/m\*K was found. To benchmark our experimental procedure we compare this value to data found in the literature. For a similar silicon sample with thickness of 50 nm Ju *et al.* [6] reported a value of k~53 W/m\*K at 300 K. On the other hand, Hao *et al.* [7] reported a value of k~32 W/m\*K at 293 K, also for 50 nm thick silicon film. Our value fits in between previously reported data.

In order to further confirm the validity of our measurement, thermal conductivity values were predicted by using an analytical model for free standing semiconducting and insulating membranes and wires [8 and references therein]. The model includes the surface scattering and the size confinement effects that phonons experience in low dimensional materials. According to this model the size-dependent thermal conductivity can be obtained as:

$$k_{l} = k_{b} P \exp\left(\frac{-\lambda}{L}\right) \left[ \exp\left(\frac{1-\alpha}{L/L_{0}-1}\right) \right]^{\frac{3}{2}}$$

(13)

Where  $k_b$  is the bulk thermal conductivity, P is a factor reflecting the surface roughness,  $\lambda$  is the phonon mean free path, L is the size nanostructure,  $\alpha$  is a material constant which relates the root-mean-square displacement of surface atoms of a crystal and that of atoms within the crystal. For free standing nanocrystals,  $\alpha = (2S_v/3R) + 1$  with the bulk vibrational entropy  $S_{\nu}$  and the ideal constant R.  $L_0$  is a critical size at which almost all atoms of a crystal are locate on its surface,  $L_0=2(3-d)w$  with the atomic/molecular diameter w and the dimension d = 0.1, and 2 for nanowires and thin films, respectively.

Table 1: Resistance and Temperature Increments Induced by a 5mA on the Heating Coil

| Coil    | R₀(Ω) (300 K)  | ΔR(Ω)       | ΔΤ(Κ)        | α (Κ <sup>-1</sup> )         |

|---------|----------------|-------------|--------------|------------------------------|

| Heating | ~1873.924±0.03 | ~2.549±0.03 | ~1.237±0.028 | ~1.1x10 <sup>3</sup> ±0.0005 |

| Sensing | ~1874.129±0.05 | ~2.491±0.05 | ~1.208±0.026 | ~1.1x10 <sup>3</sup> ±0.0006 |

| Material At 300K | K₀(W/m*K) | Р    | λ(nm) | <i>L</i> (nm) | L₀(nm)  | α      |

|------------------|-----------|------|-------|---------------|---------|--------|

| Si film          | 145       | 0.78 | 45    | 50            | 0.6736  | 2.7389 |

| Si Nanowire      | 145       | 0.45 | 45    | 50            | 0.08863 | 2.7389 |

Table 2: Parameters Used for Modeling of Si thin Films and Nanowires Using Equation (13)

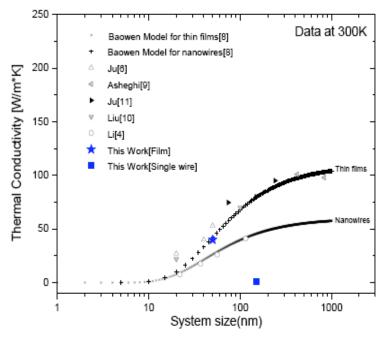

**Figure 11:** Size-dependent thermal conductivity of Si thin films at 300 K. Symbols are the experimental data previously reported and the solid star and square symbols (blue star symbol) represent the measurements obtained in this work for the film and wire respectively. The continuous upper and lower solid curves are the predictions from equation (13) with P= 0.78 and P= 0.42 for the thin film and nanowire respectively.

The formula (13) gives a quantitative prediction of the size-dependent thermal conductivity. Also it relates the thermal conductivity of a given size with the surface roughness parameter, the Knudsen number, the crystallinity length scale and the atomic vibration parameter. The surface roughness takes values  $0 < P \le 1$ . The larger value of P corresponds to smaller roughness, thus the more probability of specular scattering and viceversa. It is clear that the value of P depends greatly on the fabrication procedure of the nanostructures. Furthermore, when system size L decreases, the value of  $exp(-\lambda/L)$  also decreases, which reflects the increase of interface scattering and thus a reduced thermal conduction. There are two asymptotic limits to be satisfied by equation (13): first, if  $L \rightarrow \infty$  and  $P \rightarrow 0$ , then  $k_l \rightarrow k_b$ , second,  $L \rightarrow L_0$  or  $P \rightarrow 0$ , then  $k_l \rightarrow 0$ . Table **2** shows the parameters used in equation (13) to calculate the size-dependent thermal conductivity predictions for thin silicon films.

Figure **11** shows the size-dependent thermal conductivity of thin films from the theoretical predictions

of equation (13) and the comparison to experimental data. It is clear that predictions agree surprisingly well with the experimental data when using a roughness factor P= 0.78. This large value of P implies a small diffusive scattering contribution related to a smooth surface. Our data is also plotted (blue star) in Figure **11**. The experimental value of k~40W/m\*K is in very good agreement with equation (13). Evidently, the observed reduction in the thermal conductivity of single crystalline silicon thin film can be ascribed to the increased role of the phonon boundary scattering rather than roughness scattering.

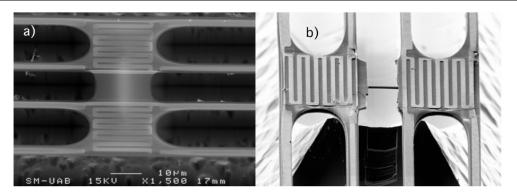

The same suspended structure is modified to evaluate the thermal conductivity of a silicon nanowire. We anticipate those nanowires will have a reduced thermal conductivity due to the atomic disorder introduced into the outer surface by the bombardment and implantation of Ga atoms from the FIB source. Figure **12a** shows the suspended Si film. The structure has not collapsed. The next step is the reduction of the silicon film into single nanowire by using focused ion

Figure 12: SEM images for suspended silicon structures. (a) shows the suspended Si film. (b) shows an image once the Si nanowire is fabricated *via* FIB from the Si film.

beam (FIB) to the desired nanoscale dimensions in order to obtain square or rectangular silicon nanowires, as shown in Figure 12b. Besides, in Figure 11 also is presented the modeling results of thermal conductivity for a Si nanowire as function of its size based on the Baowen Li model [8]. The solid square symbol (blue represents the experimental square) thermal conductivity value for a 150nmx50nm Si nanowire which is around 0.92W/m\*K at 300K. Such value is very similar to the value measured for amorphous Si, i.e. ~1W/m\*K [12]. In low dimensional structures, phonon scattering at boundaries is the main mechanism responsible for the reduction in the thermal conductivity, in contrast to Umklapp phonon scattering mechanism in bulk materials. Evidently, by observing Figure 11, the thermal conductivity value is about 50 times lower than the value predicted via modeling for a nanowire with similar size; this indicates the presence of an additional phonon scattering mechanism. Our results follow the trend outlined by Hochbaum et al. [13], and Martin et al. [14], showing the dramatic effect of the surface roughness on the thermal conductivity of nanowires. In our situation, damage to the edges and surface of the nanowire created by implantation of Ga ions during the FIB cutting process could cause stronger disruption of the lattice in these outer regions. As consequence, an additional phonon scattering mechanism on the nanowire surface due to disordered surface is present, and therefore causing an extra reduction to the thermal conductivity of the nanowire in addition to size effects.

## CONCLUSIONS

It has been demonstrated that this suspended device is well adapted for the measurement of the thermal conductance of nanoscale films and wires. Besides, the use of a FIB with nanoscale resolution permits better control of the spatial localization of the nanowires, or the fabrication of complex nanostructures without the use of masking strategies. However, it severely damages the nanostructured surface which induces a strong phonon scattering, and hence significantly reducing the thermal conductivity of the nanostructure. In spite of such damage, this strategy could be used to obtain nanostructures with low thermal conductivity which is a desirable characteristic in thermoelectric applications for thermal energy harvesting and solid state refrigeration as well.

### ACKNOWLEDGEMENTS

J.A.Q. thanks CONACYT México through Grant for fundamental research No. 130124.

This work was supported in part by the Spanish Ministerio de Innovación y Ciencia through Grants MAT2007-61521 and by the Dirección General de Recerca through 2009SGR01225.

#### REFERENCES

- Prokes SM, Stephen A. Synthesis of Si nanowires for MEMS cantilever sensor applications. Nanosensing: Materials Dev. Proceedings SPIE. 2004; 5593: 88-100. <u>http://dx.doi.org/10.1117/12.578765</u>

- [2] Chen YT, Cho YH, Takama N, Löw P, Bergaud C, Kim BJ. Simple fabrication of Si nanowire and its biological application. J Physics: Conference Series. 2009; 152: 1-7.

- [3] Shi L, Li D, Yu C, Jang W, Kim D, Yao Z, et al. Measuring thermal and thermoelectric properties of one-dimensional nanostructures using a microfabricated device. J Heat Transfer 2003; 125: 881-888. <u>http://dx.doi.org/10.1115/1.1597619</u>

- [4] Li D, Wu Y, Kim P, Shi L, Yang P, Majumdar A. Thermal conductivity of individual silicon nanowires. App Phys Lett 2003; 83(14): 2934-2936. http://dx.doi.org/10.1063/1.1616981

- [5] Gewalt A, Kalkofen B, Lisker M, Burte EP. Epitaxial growth of Si nanowires by a modified VLS method using molten Ga as growth assistant. Mater Res Soc Symp Proc 2009; 1144: LL03-11.

- [6] Ju YS. Phonon heat transport in silicon nanostructures. Appl Phys Lett 2005; 87: 153106-1-3. http://dx.doi.org/10.1063/1.2089178

[11]

[12]

[13]

[14]

3005-3007.

6131-6140.

http://dx.doi.org/10.1063/1.123994

http://dx.doi.org/10.1103/PhysRevB.46.6131

http://dx.doi.org/10.1038/nature06381

- [7] Hao Z, Zhinchao L, Lilin T, Zhimin T, Litian L, Zhijian L. Thermal conductivity measurements of ultra-thin single crystal silicon films using improved structure. 8th Inter. Confer. Solid-State Integ Circuit Tech Proc 2006: 2196-2198.

- [8] Liang LH, B Li B. Size-dependent thermal conductivity of nanoscale semiconducting systems. Phys Rev B 2006; 73: 153303-1-4. http://dx.doi.org/10.1103/PhysRevB.73.153303

- [9] Asheghi M, Leung YK, Wong SS, Goodson KE. Phononboundary scattering in thin silicon layers. Appl Phys Lett 1997; 71(13): 1798-1780. <u>http://dx.doi.org/10.1063/1.119402</u>

- [10] Liu W, Asheghi M. Phonon-boundary scattering in ultrathin single-crystal silicon layers. Appl Phys Lett 2004; 84(19): 3819-3821. <u>http://dx.doi.org/10.1063/1.1741039</u>

Received on 15-11-2014

Accepted on 25-11-2014

Published on 15-01-2015

Ju S, Goodson KE. Phonon scattering in silicon films with

thickness of order 100 nm. Appl Phys Lett 1999; 74(20):

Cahill DG, Watson SK, Pohl RO. Lower limit to the thermal

conductivity of disordered crystals. Phys Rev B 1992; 46(10):

Hochbaum AI, Chen R, Delgado RD, Liang W, Garnett EC,

Najarian M, et al. Enhanced thermoelectric performance of

Martin P, Aksamija Z, Pop E, Ravaioli U. Impact of phonon-

surface roughness scattering on thermal conductivity of thin Si nanowires. Phys Rev Lett 2009; 102: 125503-1 to -4.

rough silicon nanowires. Nature 2008; 451: 163-167.

DOI: http://dx.doi.org/10.15377/2409-5826.2015.02.01.1

© 2015 Viejo et al.; Avanti Publishers.

This is an open access article licensed under the terms of the Creative Commons Attribution Non-Commercial License (<u>http://creativecommons.org/licenses/by-nc/3.0/</u>) which permits unrestricted, non-commercial use, distribution and reproduction in any medium, provided the work is properly cited.